(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11) 特許番号

特許第6513535号 (P6513535)

(45) 発行日 令和1年5月15日(2019.5.15)

(24) 登録日 平成31年4月19日 (2019.4.19)

(51) Int.Cl.

$\mathbf{F} \mathbf{I}$

HO3L 7/24

(2006.01)

HO3L 7/24

請求項の数 5 (全 15 頁)

(21) 出願番号 (22) 出願日 特願2015-178499 (P2015-178499) 平成27年9月10日 (2015.9.10)

(65) 公開番号 (43) 公開日

審查請求日

特開2017-55295 (P2017-55295A) 平成29年3月16日 (2017.3.16) 平成30年6月13日 (2018.6.13)

(73) 特許権者 503420833 学校法人常郷

学校法人常翔学園

大阪府大阪市旭区大宮五丁目16番1号

(74)代理人 100115749

弁理士 谷川 英和

(74)代理人 100121223

弁理士 森本 悟道

(72) 発明者 吉村 勉

大阪府大阪市旭区大宮五丁目16番1号

大阪工業大学内

審査官 鬼塚 由佳

最終頁に続く

#### (54) 【発明の名称】自己注入位相同期回路

### (57) 【特許請求の範囲】

### 【請求項1】

制御電圧に応じた発振周波数の発振出力信号を出力する電圧制御発振器と、

前記発振出力信号と基準信号との位相及び周波数を比較し、当該比較の結果を示す比較結果信号を出力する位相周波数比較器と、

前記比較結果信号に応じて前記制御電圧を生成して前記電圧制御発振器に出力する電圧発生器と、

前記発振出力信号を可変な遅延時間だけ遅延させた注入信号を出力する可変遅延器と、

前記可変遅延器の遅延時間を制御する遅延制御器と、を備え、

前記注入信号は、前記電圧制御発振器に注入され、

前記遅延制御器は、前記電圧制御発振器に注入される注入信号が<u>、前記発振出力信号に対して / 2 より大きく、3 / 2 より小さい位相だけ遅れる</u>ように遅延時間を制御する、自己注入位相同期回路。

## 【請求項2】

前記注入信号を前記電圧制御発振器に注入するかどうかを切り替える切替器と、

前記注入信号が、前記発振出力信号が前記基準信号に同期するまでは注入されず、同期した後に注入されるように前記切替器を制御する注入制御器と、をさらに備えた、請求項 1記載の自己注入位相同期回路。

#### 【請求項3】

前記可変遅延器から出力された注入信号の強度及びパルス幅の少なくとも一方を変更した

10

注入信号を出力するパルス発生器をさらに備えた、請求項1または請求項2記載の自己注入位相同期回路。

### 【請求項4】

前記発振出力信号を分周し、分周後の発振出力信号を前記位相周波数比較器及び前記可変 遅延器に出力する分周器をさらに備え、

前記パルス発生器は、前記可変遅延器から出力された注入信号のパルス幅を少なくとも変更する、請求項3記載の自己注入位相同期回路。

### 【請求項5】

前記パルス発生器は、前記可変遅延器から出力された注入信号の強度を少なくとも変更するものであり、

前記発振出力信号を用いてノイズ量を検出するノイズ検出器と、

前記ノイズ検出器によって検出されたノイズ量に応じた強度の注入信号が出力されるよう に前記パルス発生器を制御する強度制御器と、をさらに備え、

前記パルス発生器から出力される注入信号の強度は、検出されたノイズ量が多いほど大きくなり、検出されたノイズ量が少ないほど小さくなるように前記強度制御器によって制御される、請求項3または請求項4記載の自己注入位相同期回路。

【発明の詳細な説明】

### 【技術分野】

### [0001]

本発明は、位相同期回路において負帰還となるように自己注入を行う自己注入位相同期 20回路に関する。

### 【背景技術】

### [0002]

従来、発振器に発振周波数に極めて近い摂動を与えて、その印加信号に同期させるインジェクションロックが知られており、集積回路においては、1970年代のAdlerらの研究がある(非特許文献1参照)。

### [0003]

近年、自己注入(self injection)を用いた発振回路についても研究されており、位相同期回路(PLL: Phase Locked Loop)において、自己注入同期を行うことも行われている(非特許文献 2 参照)。その非特許文献 2 に記載されている自己注入同期においては、発振器からの発振信号を遅延ケーブルで遅延させ、帰還位相を移相器で調整した上で発振器に注入することが行われている。

# 【先行技術文献】

### 【非特許文献】

### [0004]

【非特許文献 1 】 R. Adler, "A Study of Locking Phenomena in Oscillators," Proc. I EEE, vol.61, pp.1380 1385, Oct. 1973

【非特許文献 2 】堤恒次、都留正臣、谷口英司、「SiGe BiCMOSによる自己注入同期VCO内蔵PLL IC」、2012年電子情報通信学会エレクトロニクスソサイエティ大会,C 2 2 , p.28 , 2012年

#### 【発明の概要】

### 【発明が解決しようとする課題】

### [0005]

しかしながら、上記非特許文献 2 に記載されている自己注入同期においては、移相器による位相の調整を手動で行う必要があった。そのため、位相同期回路ごとに移相器を調整したり、発振周波数が変更されるごとに移相器を調整したりする必要があり、その調整のための作業が煩雑であるという問題があった。また、その調整が不適切であった場合、例えば、正帰還による注入が行われることになった場合には、注入の効果が得られないという問題もあった。

# [0006]

40

10

本発明は、上記課題を解決するためになされたものであり、適切な位相での自己注入を自動的に実現できる自己注入位相同期回路を提供することを目的とする。

#### 【課題を解決するための手段】

#### [0007]

上記目的を達成するため、本発明による自己注入位相同期回路は、制御電圧に応じた発振周波数の発振出力信号を出力する電圧制御発振器と、発振出力信号と基準信号との位相及び周波数を比較し、比較の結果を示す比較結果信号を出力する位相周波数比較器と、比較結果信号に応じて制御電圧を生成して電圧制御発振器に出力する電圧発生器と、発振出力信号を可変な遅延時間だけ遅延させた注入信号を出力する可変遅延器と、可変遅延器の遅延時間を制御する遅延制御器と、を備え、注入信号は、電圧制御発振器に注入され、遅延制御器は、電圧制御発振器に注入される注入信号が負帰還となるように遅延時間を制御する、ものである。

このような構成により、注入信号を負帰還で電圧制御発振器に注入することを、遅延制御器によって自動的に実現することができ、作業者等による位相の調整の作業が不要になる。また、そのような自己注入を行うことによって、発振出力信号の位相ノイズを低減することができる。なお、電圧制御発振器から出力された発振出力信号は、分周されることなく位相周波数比較器に入力されてもよく、または、分周されて位相周波数比較器に入力されてもよい。後者の場合には、基準信号の周波数に分周比を掛けた周波数の発振出力信号を出力することができるようになる。

### [0008]

また、本発明による自己注入位相同期回路では、注入信号を電圧制御発振器に注入するかどうかを切り替える切替器と、注入信号が、発振出力信号が基準信号に同期するまでは注入されず、同期した後に注入されるように切替器を制御する注入制御器と、をさらに備えてもよい。

このような構成により、発振周波数が安定していない状況で自己注入を行うことによって発振出力信号が不安定になることを回避することができる。

#### r n n n a 1

また、本発明による自己注入位相同期回路では、可変遅延器から出力された注入信号の強度及びパルス幅の少なくとも一方を変更した注入信号を出力するパルス発生器をさらに備えてもよい。

このような構成により、例えば、適切な自己注入を実現するために、注入信号の強度や パルス幅を変更することができるようになる。

### [0010]

また、本発明による自己注入位相同期回路では、発振出力信号を分周し、分周後の発振出力信号を位相周波数比較器及び可変遅延器に出力する分周器をさらに備え、パルス発生器は、可変遅延器から出力された注入信号のパルス幅を少なくとも変更してもよい。

このような構成により、分周器によって分周された信号を用いて自己注入を行うことによって、例えば、回路の簡略化や省電力化を実現することができる。また、分周によってパルス幅が変化するが、そのパルス幅を、パルス発生器によって適切なものにすることができる。その結果、例えば、スプリアスノイズを低減させることができる。

#### [0011]

また、本発明による自己注入位相同期回路では、パルス発生器は、可変遅延器から出力された注入信号の強度を少なくとも変更するものであり、発振出力信号を用いてノイズ量を検出するノイズ検出器と、ノイズ検出器によって検出されたノイズ量に応じた強度の注入信号が出力されるようにパルス発生器を制御する強度制御器と、をさらに備え、パルス発生器から出力される注入信号の強度は、検出されたノイズ量が多いほど大きくなり、検出されたノイズ量が少ないほど小さくなるように強度制御器によって制御されてもよい。

このような構成により、ノイズ量が多い場合には、注入信号の強度を大きくすることによって、注入の影響を大きくすることができ、その結果、位相ノイズを低減させることができる。一方、注入信号の強度を大きくするとスプリアスノイズが発生するため、ノイズ

20

30

40

5

20

40

量が少ない場合には、注入信号の強度を小さくすることによって、注入の影響を小さくすることができ、スプリアスノイズを低減させることができる。

#### 【発明の効果】

#### [0012]

本発明による自己注入位相同期回路によれば、適切な位相での自己注入を自動的に実現することができるようになる。

### 【図面の簡単な説明】

### [0013]

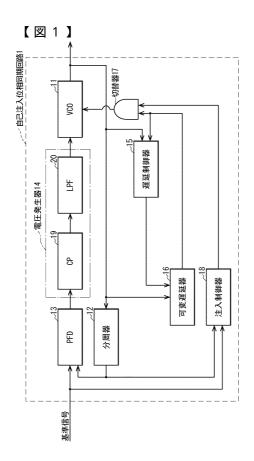

- 【図1】本発明の実施の形態による自己注入位相同期回路の構成を示すブロック図

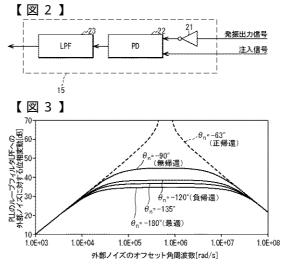

- 【図2】同実施の形態における遅延制御器の構成を示すブロック図

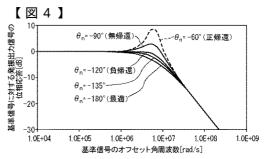

- 【図3】同実施の形態における外部ノイズの影響を示すグラフ

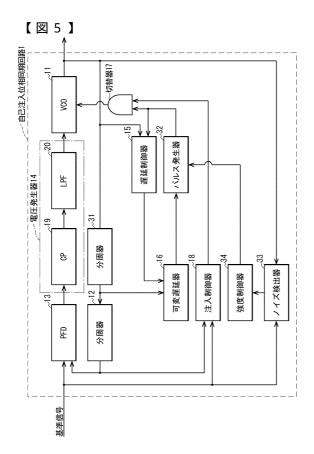

- 【図4】同実施の形態における基準信号に対する発振出力信号の周波数特性を示すグラフ

- 【図5】同実施の形態による自己注入位相同期回路の他の構成を示すブロック図

#### 【発明を実施するための形態】

#### [0014]

以下、本発明による自己注入位相同期回路について、実施の形態を用いて説明する。なお、以下の実施の形態において、同じ符号を付した構成要素は同一または相当するものであり、再度の説明を省略することがある。本実施の形態による自己注入位相同期回路は、位相同期回路において負帰還となるように自己注入(自己インジェクション)を行うものであり、その自己注入に用いる注入信号の位相を自動的に制御するものである。

#### [0015]

図1は、本実施の形態による自己注入位相同期回路1の構成を示すブロック図である。本実施の形態による自己注入位相同期回路1は、電圧制御発振器(VCO: Voltage Cont rolled Oscillator) 11と、分周器12と、位相周波数比較器(PFD: Phase Frequen cy Detector) 13と、電圧発生器14と、遅延制御器15と、可変遅延器16と、切替器17と、注入制御器18と、を備える。

### [0016]

電圧制御発振器11は、電圧発生器14からの制御電圧に応じた発振周波数の発振出力信号を出力する。この電圧制御発振器11の種類は問わないが、例えば、LCタンク発振器であってもよく、LCクロスカップル型発振器であってもよく、その他の種類の電圧制御発振器であってもよい。また、電圧制御発振器11には、自己注入のための注入信号が注入される。その注入信号を電圧制御発振器11に注入する方法は問わない。その注入信号を電圧制御発振器11に注入する方法としては、例えば、注入信号の電流を直接、電圧制御発振器11に注入する方法(direct current injection)や、注入信号のパルスを電圧制御発振器11に注入する方法(capacitive coupling injection)などがある。その注入方法の具体例については、例えば、次の文献を参照されたい。

文献: S. Morishita, S. Shimizu, T. Kihara, T. Yoshimura, "Subharmonically Injection Locked PLL with Variable Pulse Width Injections," ISCAS 2015, pp.557 560, May 2015

### [0017]

分周器12は、電圧制御発振器11から出力された発振出力信号を所定の分周比nで分周し、分周後の発振出力信号を位相周波数比較器13と、注入制御器18とに出力する。この分周器12によって、発振出力信号の周波数が1/nにされる。なお、nは正の整数である。分周器12は、分周比nを変更可能なものであってもよく、または、そうでなくてもよい。

#### [0018]

位相周波数比較器 1 3 は、発振出力信号と、基準信号との位相及び周波数を比較し、その比較の結果を示す比較結果信号を出力する。基準信号は、自己注入位相同期回路において、発振出力信号を同期させる対象となる信号(参照信号)であり、例えば、水晶発振器等によって発振された安定した低位相ノイズの信号であることが好適である。なお、自己

注入位相同期回路1は分周器12を有するため、基準信号と比較される発振出力信号は、 分周器12によって分周された発振出力信号となる。位相周波数比較器13の構成は特に 限定されないが、例えば、発振出力信号と基準信号との立ち上がりエッジの差を示す比較 結果信号を出力するものであってもよい。

#### [0019]

電圧発生器 1 4 は、位相周波数比較器 1 3 から出力された比較結果信号に応じて制御電圧を生成して電圧制御発振器 1 1 に出力する。その電圧発生器 1 4 は、チャージポンプ(CP: Charge Pump) 1 9 と、ループフィルタ(LPF: Loop Filter) 2 0 とを備える。

### [0020]

チャージポンプ19は、位相周波数比較器13から出力された比較結果信号を電流または電圧に変換してループフィルタ20に出力する。すなわち、チャージポンプは、電流チャージ型であってもよく、電圧チャージ型であってもよい。このチャージポンプ19によって、位相周波数比較器13によって検出された両信号の比較結果が、電流パルスや電圧パルスに変換されることになる。

#### [0021]

ループフィルタ 2 0 は、チャージポンプ 1 9 によって変換された電流または電圧に応じて制御電圧を生成して電圧制御発振器 1 1 に出力する。ループフィルタ 2 0 は、チャージポンプ 1 9 からの出力を平滑化して出力するローパスフィルタである。

### [0022]

なお、本実施の形態では、電圧発生器14が、チャージポンプ19及びループフィルタ 20を有する場合について説明するが、そうでなくてもよい。電圧発生器14は、比較結 果信号に応じた制御電圧を電圧制御発振器11に出力するものであればよく、その構成は 問わない。すなわち、PLLにおいて、位相周波数比較器13と電圧制御発振器11との 間に存在する構成が電圧発生器14であると考えてもよい。PLLが集積回路上に構成さ れる場合には、電圧発生器14は、通常、チャージポンプ19とループフィルタ20とを 有することが多いが、PLLがディスクリートに構成される場合には、チャージポンプ1 9とループフィルタ20とを有する以外の電圧発生器14として、OPアンプを用いた積 分器(アクティブ・フィルタ)として動作し、比較結果信号に相当する電圧をサンプル・ ホールドする回路などを用いることもできる。なお、ループフィルタをオペアンプなどを 用いたアクティブフィルタとした場合、オペアンプを構成しているトランジスタの内部ノ イズがPLLの出力クロックの位相ノイズの原因になることがある。また、PLLが集積 回路上に構成される場合には、オペアンプも回路内部にあるためにPLLの動作に伴う電 源ノイズの影響を受けやすいと考えられる。一方、チャージポンプ方式にした場合、ルー プフィルタは単純な抵抗と容量の組み合わせで構成できる。そのようにループフィルタを 単純化することにより、フィルタ回路による上記ノイズの影響を受けにくいと考えられる 。そのような観点から、PLLを含む回路が集積回路上に構成される場合は、チャージポ ンプ方式が特に好ましい。

# [0023]

また、図1で示されるPLLの位相周波数比較器13やチャージポンプ19等の構成は便宜上、そのように記載したものであって、任意の2以上の構成が一体に構成されていてもよい。例えば、位相周波数比較器13とチャージポンプ19とが一体に構成されていてもよく、チャージポンプ19とループフィルタ20とが一体に構成されていてもよい。

### [0024]

遅延制御器15は、可変遅延器16の遅延時間を制御する。すなわち、遅延制御器15は、電圧制御発振器11に注入される注入信号が負帰還となるように遅延時間を制御する。電圧制御発振器11に注入される注入信号が、発振出力信号に対して / 2より大きく、3 / 2より小さい位相だけ遅れると、負帰還の注入が行われることになる。したがって、遅延制御器15は、その範囲内となるように遅延時間を制御することが好適である。なお、後述するように、電圧制御発振器11に注入される注入信号が、発振出力信号に対して だけ位相が遅れると、最適の負帰還での注入となる。したがって、遅延制御器15

は、注入信号が発振出力信号に対して だけ位相が遅れるように可変遅延器 1 6 を制御するようにしてもよい。具体的な制御方法については、図 2 を用いて後述する。

#### [0025]

可変遅延器 1 6 は、電圧制御発振器 1 1 から出力された発振出力信号を、可変な遅延時間だけ遅延させた注入信号を出力する。その遅延時間は、遅延制御器 1 5 によって制御される。また、可変遅延器 1 6 から出力された注入信号は、切替器 1 7 を介して電圧制御発振器 1 1 に注入される。可変遅延器 1 6 は、例えば、制御電圧に応じた遅延時間だけ発振出力信号を遅延させるものであってもよい。

#### [0026]

なお、遅延制御器15及び可変遅延器16は、いわゆるDLL(Delay Locked Loop)と同様に構成されてもよく、または、そうでなくてもよい。本実施の形態では、遅延制御器15及び可変遅延器16が、DLLと同様に構成される場合について主に説明する。

#### [0027]

切替器17は、可変遅延器16からの注入信号を電圧制御発振器11に注入するかどうかを切り替える。その切り替えは、注入制御器18による制御によって行われる。図1で示されるように、切替器17がAND回路で構成されるとすると、注入制御器18からの注入イネーブル信号が「1」である場合には、可変遅延器16からの注入信号が電圧制御発振器11に注入されることになり、注入イネーブル信号が「0」の場合、すなわち注入イネーブル信号が出力されていない場合には、注入信号が電圧制御発振器11に注入されないことになる。なお、切替器17は、AND回路以外の開閉器等によって構成されてもよいことは言うまでもない。

#### [0028]

注入制御器18は、発振出力信号が基準信号に同期するまでは注入信号が電圧制御発振 器11に注入されず、発振出力信号が基準信号に同期した後には注入信号が電圧制御発振 器11に注入されるように切替器17を制御する。注入制御器18によって、PLLが基 準信号にロックした後に自己注入が行われるようにすることで、発振周波数がまだ安定し ていないときに注入が行われることを防止できる。その結果、発振周波数が不安定なとき に注入が行われ、発振出力信号が不安定になることを回避することができる。なお、上述 のように、切替器17がAND回路である場合には、注入制御器18は、発振出力信号が 基準信号に同期するまでは注入イネーブル信号「0」を出力し、同期後は注入イネーブル 信号「1」を出力してもよい。また、注入イネーブル信号「0」を出力するとは、注入イ ネーブル信号を出力しないことであると考えてもよい。また、注入制御器18が、発振出 力信号が基準信号に同期したかどうかを判断する方法は問わない。例えば、注入制御器1 8は、発振出力信号と基準信号との比較結果に応じて両者が同期したことを検知してもよ い。その比較結果は、位相周波数比較器13による比較結果を用いてもよく、または、注 入制御器18において比較を行ってもよい。本実施の形態では、後者の場合について主に 説明する。また、例えば、注入制御器18は、PLLが動作を開始してからあらかじめ決 められた時間が経過した場合に、両者が同期したとしてもよい。具体的には、注入制御器 18は、PLLの動作開始時からの基準信号のクロックカウント値があらかじめ決められ た値になった際に、あらかじめ決められた時間が経過したとしてもよい。なお、回路の動 作中に分周器12が分周比を変更可能である場合には、注入制御器18は、分周器12が 分周比を変更した後においても、発振出力信号が基準信号に同期するまでは注入信号が電 圧制御発振器11に注入されず、発振出力信号が基準信号に同期した後には注入信号が電 圧制御発振器11に注入されるように切替器17を制御することが好適である。なお、注 入制御器18が同期の検知に応じて制御している場合には、分周比が変更された際にも同 期するまでは注入が行われないことになる。一方、動作の開始時からの経過時間に応じて 制御を行っている場合には、注入制御器18は、例えば、分周比が変更された際に、注入 信号が電圧制御発振器11に注入されないように切替器17を制御し、その変更時からあ らかじめ決められた時間が経過した後に、両者が同期したとして、注入信号が電圧制御発

振器11に注入されるように切替器17を制御してもよい。また、注入信号が電圧制御発

振器 1 1 に注入されないように制御するとは、自己注入とならないように制御することである。したがって、その制御は、通常、注入信号を電圧制御発振器 1 1 に入力しないようにすることであるが、自己注入とならない程度の注入信号、すなわち非常に小さい強度の注入信号を電圧制御発振器 1 1 に入力することを含むと考えてもよい。

#### [0029]

図 2 は、本実施の形態による遅延制御器 1 5 の構成を示すブロック図である。図 2 において、遅延制御器 1 5 は、N O T 回路 2 1 と、位相比較器 ( P D : Phase Detector ) 2 2 と、ループフィルタ ( L P F ) 2 3 とを備える。

### [0030]

NOT回路21は、電圧制御発振器11から出力された発振出力信号を反転させる。この反転によって、発振出力信号の位相が (180°)だけ移相されることになる。発振出力信号を反転させるのは、電圧制御発振器11に注入される注入信号と、電圧制御発振器11から出力される発振出力信号との位相を だけ異なるようにするためである。両信号の位相差を にすることによって、注入信号を負帰還で注入することができ、また後述するように、最適な注入とすることができるようになる。

#### [0031]

位相比較器 2 2 は、電圧制御発振器 1 1 から出力され、NOT回路 2 1 によって反転された発振出力信号と、可変遅延器 1 6 から出力された注入信号との位相を比較し、その比較の結果を示す信号を出力する。なお、位相比較器 2 2 は、位相周波数比較器であってもよいが、ここでは両信号の位相の比較ができれば十分であるため、周波数の比較を行わないものであってもよい。また、位相比較器 2 2 は、例えば、ミキサなどの位相検波器であってもよい。

# [0032]

ループフィルタ23は、位相比較器22から出力された信号に応じて、可変遅延器16 を制御する信号を生成して可変遅延器16に出力する。なお、ループフィルタ23が出力 する信号は、可変遅延器16の制御電圧であってもよい。

### [0033]

なお、図2で示される遅延制御器15と可変遅延器16とのうち、NOT回路21以外の構成によって、DLLが構成されることになる。また、そのNOT回路21が存在することによって、通常のDLLとは異なり、発振出力信号と注入信号とに の位相差が生じることになる。また、遅延制御器15において、PLLと同様に、位相比較器22とループフィルタ23との間に、チャージポンプを備えるようにしてもよい。また、図2では、発振出力信号をNOT回路21で反転する構成について示しているが、注入信号をNOT回路21で反転してもよい。その場合にも、注入信号の位相を、発振出力信号に対してだけずらすことができる。また、NOT回路21を用いた場合には、注入信号と、発振出力信号との位相差が になる。したがって、それ以外の位相差にしたい場合には、NOT回路21に代えて、または、NOT回路21と共に、位相比較器22への入力の少なくとも一方を遅延させる遅延器や移相器等を用いるようにしてもよい。なお、注入信号と発振出力信号との位相差が 以外に制御される場合であっても、少なくとも注入信号が負帰還で注入される範囲の位相差に制御されるものとする。

#### [0034]

次に、自己注入位相同期回路1の動作について簡単に説明する。自己注入位相同期回路1における処理が開始されると、PLLにおいて、電圧制御発振器11によって出力される発振出力信号が基準信号にロックするように制御される。なお、その開始時点では、注入制御器18から出力される注入イネーブル信号が「0」となっているため、切替器17の出力も「0」となり、電圧制御発振器11への注入は行われないことになる。

# [0035]

その後、電圧制御発振器11が出力する発振出力信号が基準信号に同期すると、注入制御器18は、注入イネーブル信号を「0」から「1」に切り替える。その結果、可変遅延器16から出力された注入信号が電圧制御発振器11に注入されるようになる。その注入

信号は、前述のように、発振出力信号の位相を だけずらした信号を用いたDLLの結果であるため、発振出力信号と位相が だけ異なることになり、負帰還で電圧制御発振器11に注入されることになる。電圧制御発振器11では、電圧発生器14から出力される制御電圧と、可変遅延器16から出力される負帰還の注入信号とに応じて発振出力信号が出力されることになる。その結果、位相ノイズが低減されることになる。

### [0036]

ここで、ループフィルタ 2 0 と電圧制御発振器 1 1 との間に相当するノードに外部ノイズを印加したシミュレーション結果について説明する。図 3 は、そのシミュレーションにおける外部ノイズのオフセット角周波数(横軸)と、PLLのループフィルタLPFへの外部ノイズに対する発振出力信号における位相変動の程度(縦軸)との関係を示すグラフである。なお、図 3 のグラフにおける 」は、可変遅延器 1 6 によって遅延された位相(deg)である。なお、」が - 6 3 °よりも大きくなると発散した。図 3 の結果から、負帰還の場合には、無帰還の場合には、無帰還の場合には、無帰還の場合には、無帰還の場合よりも誤差が大きくなっていることがわかる。一方、正帰還の場合には、無帰還の場合よりも誤差が大きくなっている。そのことから、遅延制御器 1 5 による、負帰還にするための位相制御(遅延時間の制御)が重要であることがわかる。また、発振出力信号と注入信号との位相差がである場合に、最適な負帰還となることがわかる。したがって、本実施の形態では、遅延制御器 1 5 において、位相比較器 2 2 に入力される信号のうち、一方をNOT回路 2 1 で反転させている。

### [0037]

次に、基準信号に対する発振出力信号の周波数特性に関するシミュレーション結果についても説明する。図4は、そのシミュレーションにおいて、基準信号のオフセット角周波数(横軸)と、基準信号に対する発振出力信号の位相応答(縦軸)との関係を示すグラフである。図4のグラフにおける。も、図3のグラフと同様のものである。図4のグラフにおいて、「ニー90°、-60°においては、入出力特性にピークが生じている。そのようなピークが存在するとノイズの原因になるため、通常、ループフィルタ20を構成しているコンデンサ等の部品の容量を大きくすることにより、すなわちループフィルタ20のサイズを大きくすることによって、ピークを下げることになる。一方、本実施の形態による自己注入位相同期回路1のように、負帰還で自己注入を行った場合には、そのよるときには、ピークが生じていない。そのよるとつがインを抑えることができる。このシミュレーション結果では、特に基準信号との、ループフィルタ20の設計に自由度が生まれることになる。具体的には、ダンピングインを抑制することができるため、ループフィルタ20を横成している部品の容量を削減することができ、ループフィルタ20のサイズを小さくできるようになる。

#### [ 0 0 3 8 ]

なお、本実施の形態による自己注入位相同期回路1において、電圧制御発振器11に注入する注入信号の強度やパルス幅を変更するようにしてもよい。図5は、そのような自己注入位相同期回路1の構成の一例を示すブロック図である。図5において、自己注入位相同期回路1は、電圧制御発振器11と、分周器12と、位相周波数比較器13と、電圧発生器14と、遅延制御器15と、可変遅延器16と、切替器17と、注入制御器18と、分周器31と、パルス発生器32と、ノイズ検出器33と、強度制御器34とを備える。分周器31、パルス発生器32、ノイズ検出器33、強度制御器34以外の構成及び動作については、上述の説明と同様であり、その詳細な説明を省略する。

### [0039]

分周器 3 1 は、電圧制御発振器 1 1 から出力された発振出力信号を所定の分周比mで分周し、分周後の発振出力信号を分周器 1 2 と、可変遅延器 1 6 とに出力する。この場合には、分周器 3 1 と分周器 1 2 とによって分周されるため、発振出力信号の周波数は 1 / (n×m)になって位相周波数比較器 1 3 に入力されることになる。なお、mは正の整数である。そのmは、大きな値でないことが好適である。例えば、分周器 3 1 によって分周さ

れた発振出力信号を遅延させた注入信号に応じた注入を行うと、分周器31が存在しなかった場合と比較して、電圧制御発振器11に注入されるパルスの頻度が1/mとなる。その頻度が少なくなりすぎると、注入信号に同期させることが困難になるからである。mは、8以下であることが好適であり、4以下であることがより好適である。この分周器31を備えることによって、発振出力信号とは独立して、自己注入の周波数を決めることができるようになる。なお、分周器31によって分周された発振出力信号に応じた注入信号が電圧制御発振器11に注入される場合には、その注入信号の注入が発振出力信号の周期ごとに行われるのではなく、飛び飛びに行われることになる。したがって、その場合には、注入信号のパルスを注入する方法(capacitive coupling injection)によって電圧制御発振器11に対する注入が行われることが好適である。分周器31は、分周比mを変更可能なものであってもよく、または、そうでなくてもよい。

### [0040]

パルス発生器 3 2 は、可変遅延器 1 6 から出力された注入信号の強度及びパルス幅の少なくとも一方を変更した注入信号を出力する。注入信号の強度とは、注入信号に含まれるパルスの振幅である。注入信号のパルス幅とは、注入信号に含まれるパルスの立ち上がり時点から立ち下がり時点までの時間的な長さである。なお、パルス発生器 3 2 に入力される注入信号と、パルス発生器 3 2 から出力される注入信号との位相は同じであることが好適である。位相が同じであるとは、注入信号に含まれるパルスの立ち上がりのタイミングが一致していることであってもよい。本実施の形態では、パルス発生器 3 2 が、注入信号の強度及びパルス幅の両方を調整する場合について主に説明する。

#### [0041]

パルス発生器 3 2 がパルス幅を変更する場合には、変更後のパルス幅は、発振出力信号の周期の半整数の長さとなることが好適である。そのようにすることで、スプリアスノイズを低減することができるからである。例えば、変更後のパルス幅は、発振出力信号の半周期の長さであってもよい。分周器 3 1 が存在する場合には、その分周によって可変遅延器 1 6 から出力される注入信号のパルス幅が大きくなるため、パルス発生器 3 2 によって、そのパルス幅が小さくなるように調整してもよい。

### [0042]

ノイズ検出器33は、電圧制御発振器11から出力された発振出力信号を少なくとも用 いてノイズ量を検出する。ノイズ検出器33は、図5で示されるように、基準信号をも用 いてノイズ量を検出してもよい。そのノイズ量は、ノイズの程度を知ることができるもの であり、例えば、発振出力信号のジッタ量であってもよく、発振出力信号の周波数スペク トルにおいて、中心周波数から所定のオフセット周波数だけ離れた周波数における信号強 度であってもよく、ノイズの量を知ることができるその他の値であってもよい。中心周波 数とは、発振出力信号の理想的な周波数であり、中心周波数をfゥとし、基準信号の周波 数をf₁とすると、f₀=f₁xnxmとなる。なお、n,mは、上述の分周比である。 したがって、オフセット周波数をfゕとすると、ノイズ量は、周波数スペクトルにおける fぃ±f灬の値となる。なお、その2個の値のうち、いずれか一方のみをノイズ量として 用いてもよく、または、両方を用いてもよい。後者の場合には、例えば、2個の値の代表 値をノイズ量としてもよく、2個の値の合計値をノイズ量としてもよい。代表値は、例え ば、平均値、最大値、最小値であってもよい。ノイズ量がジッタ量である場合には、ノイ ズ検出器33は、ジッタを測定できる機器、例えば、オシロスコープ(ジッタモニタ)で あってもよい。ノイズ検出器33がオシロスコープである場合には、ノイズ検出器33に 基準信号も入力されることが好適である。また、ノイズ量が周波数スペクトルにおけるf 。± f mの値である場合には、ノイズ検出器33は、周波数スペクトルを取得するスペク トラムアナライザと、そのスペクトラムアナライザによって取得された周波数スペクトル において、fotfmのノイズ量を取得する構成とを有するものであってもよい。

### [0043]

強度制御器 3 4 は、ノイズ検出器 3 3 によって検出されたノイズ量に応じた強度の注入信号が出力されるようにパルス発生器 3 2 を制御する。その制御において、強度制御器 3

4 は、検出されたノイズ量が多いほど、電圧制御発振器11に注入される注入信号の強度 が大きくなり、検出されたノイズ量が少ないほど、電圧制御発振器11に注入される注入 信号の強度が小さくなるように制御してもよい。強度制御器34は、検出されたノイズ量 に対応する注入信号の強度を特定する際に、例えば、ノイズ量と注入信号の強度とを対応 付けるテーブル等の情報を用いてもよく、ノイズ量を引数とする関数を用いてもよい。ノ イズ量と注入信号の強度とを対応付ける情報において、ノイズ量が多くなるほど、注入信 号の強度が大きくなるように両者が対応付けられているものとする。また、ノイズ量を引 数とする関数は、ノイズ量に対する増加関数であり、その関数の値が注入信号の強度とな るものであることが好適である。なお、増加関数は、単調非減少関数であると考えてもよ い。このような制御を行うことにより、外部ノイズなどのノイズが多い場合に注入の影響 を大きくすることができ、その結果、位相ノイズを低減させることができる。一方、注入 信号の強度を大きくするとスプリアスノイズが大きくなるため、外部ノイズなどのノイズ が少ない場合には、注入の影響を小さくすることによって、スプリアスノイズを低減させ ることができる。また、そのような注入信号の強度に関する制御は、外部ノイズ以外に起 因する位相ノイズ、すなわちPLL自体の位相ノイズを低減するためにも有効であると考 えられる。また、そのようにしてPLLを安定化させることに応じて、ループフィルタ 2 0の容量を削減させることも可能になり得る。

#### [0044]

なお、発振出力信号をモニタしてPLLの応答を最適化する方法としては、PLLのループ帯域やノイズ源(例えば、出力ドライバなど)の動作タイミングを変更することなどが考えられる。しかしながら、PLLのループ帯域は、基準信号のジッタ抑圧効果や、分周比の設定などを考慮して決める必要があり、調整幅に限界がある。また、ノイズ源のタイミング変更については、ノイズ源が明らかになっている場合にはある程度、行うことができるが、多くの場合にはそのノイズ源の特定は困難であり、現実的には行うことが難しい。一方、強度制御器34によって注入信号の強度を制御することによって、PLLのループ帯域やノイズ源の動作タイミングを変更することなく、外部ノイズに対する応答を調整することができるようになるメリットがある。

# [0045]

また、図5で示される自己注入位相同期回路1においては、可変遅延器16に入力される発振出力信号を分周しているため、遅延制御器15では、図2で示されるように、注入信号ではなく、発振出力信号を反転させて位相比較器22に入力することが好適である。また、図5で示される自己注入位相同期回路1において、パルス発生器32によってパルス幅を変更する場合には、遅延制御器15に入力される注入信号のデューティー比(HとLとの比)が50%にはならないため、位相比較器22は、ミキサ型ではないことが好適である。

# [0046]

また、図5では、自己注入位相同期回路1が分周器31を備えている場合について説明したが、そうでなくてもよい。自己注入位相同期回路1は、分周器31を備えていなくてもよい。その場合には、パルス発生器32において、パルス幅の調整が行われなくてもよい。なお、分周器31が存在しない場合であっても、パルス発生器32は、パルス幅を調整してもよい。その場合には、例えば、操作者等が、パルス発生器32が発生するパルスのパルス幅を調整(設定)するようにしてもよい。

# [0047]

また、図5では、自己注入位相同期回路1がノイズ検出器33及び強度制御器34を備えている場合について説明したが、そうでなくてもよい。自己注入位相同期回路1は、ノイズ検出器33及び強度制御器34を備えていなくてもよい。その場合には、パルス発生器32において、パルスの強度の調整が行われなくてもよい。なお、ノイズ検出器33及び強度制御器34が存在しない場合であっても、パルス発生器32は、パルスの強度を調整してもよい。その場合には、例えば、操作者等が、パルス発生器32が発生するパルスの強度を調整(設定)するようにしてもよい。例えば、 n=-180°の負帰還におい

て、図4の位相応答を得たときよりも強度の大きい注入信号を注入すれば、図4における n=-180°の特性曲線よりも、コーナーの箇所においてさらに下の方(応答が小さくなる方向)の特性曲線となり、ノイズの抑制効果がさらに大きくなる。したがって、求められるノイズの抑制の程度に応じた強度のパルスが生成されるように、パルス発生器32を調整してもよい。

### [0048]

以上のように、本実施の形態による自己注入位相同期回路1によれば、位相同期回路に おいて負帰還の自己注入を行うことによって、位相ノイズを低減させることができる。ま た、その負帰還の自己注入によって、外部ノイズに対するロバスト性も向上していること がわかる。さらに、周波数特性におけるピークゲインを抑制することもできるため、ルー プフィルタ20の容量を削減することも可能となる。また、自己注入VCOを有する同期 回路において、注入信号の発振出力信号に対する遅延量、すなわち注入信号の位相を自動 的に調整することができるため、作業者等が位相を調整する必要がなく、作業者の負担が 軽減されることになる。特に、PLLの分周比や基準信号の周波数が変更された場合でも 、変更後の周波数に応じた遅延量となるように適切に自動的に調整されることになり、分 周比や周波数が変更されるごとに手動で遅延量を調整する必要がないことになる。また、 そのような遅延量の自動調整が行われることによって、位相ノイズなどの影響で発振出力 信号の周期が微少量だけ変化した場合であっても、それに応じて遅延量が変更されること になり、例えば、発振出力信号に対する移相量が である注入信号を注入することができ る。その結果、位相ノイズの低減効果が高くなる。また、注入制御器18を備えたことに よって、発振周波数が安定していない状況において自己注入が行われることによって発振 出力信号が不安定になることを回避できる。また、可変遅延器16に入力される発振出力 信号を分周した場合には、回路の簡略化や省電力化を実現することができる。また、検出 されたノイズ量に応じた強度の注入信号を注入することによって、ノイズ量が多い場合で あっても、位相ノイズを低減させることができ、また、ノイズ量が少ない場合におけるス プリアスノイズを低減させることができる。

### [0049]

なお、本実施の形態による自己注入位相同期回路1は、例えば、Integer‐N及びFractional‐Nクロック生成回路におけるループ帯域のノイズ低減手法とって用いることが可能である。Integer‐Nクロック生成回路では、PLLのルーの帯域を基準信号の周波数の数十分の1から数分の1以下に抑える必要がある。なぜなら、これよりループ帯域を大きくすると、位相周波数比較器の出力変動がPLLの動作に影響を与え、クロック出力が不安定になるからである。具体的には、クロック出力が周期的に、クロック出力が不安定になるからである。具体的には、クロック出力が周期にまた、Fractional‐Nクロック生成回路についても同様であり、さらにループ帯域に関して制限が大きくなる。一方、本実施の形態による自己注入位相同期回路1は、日のようなPLLのループ帯域付近のノイズに対する抑制効果を有しているため、PLLのループ帯域を小さくても、出力クロックに変動が起こらない間によいまである。ロープである。カランシーバ回路によいて開いることができる。

### [0050]

また、本実施の形態では、自己注入位相同期回路 1 が切替器 1 7 及び注入制御器 1 8 を備えている場合について説明したが、そうでなくてもよい。自己注入位相同期回路 1 は、切替器 1 7 及び注入制御器 1 8 を備えていなくてもよい。その場合には、PLLがロックするまでの期間が長くなり得るが、ロック後は、上述の自己注入位相同期回路 1 と同様のものとなる。

### [0051]

また、本実施の形態では、自己注入位相同期回路1が分周器12を備えている場合につ

いて説明したが、そうでなくてもよい。自己注入位相同期回路1は、分周器12を備えていなくてもよい。その場合には、図1において、電圧制御発振器11から出力された発振出力信号が位相周波数比較器13と注入制御器18とに入力されてもよく、図5において、分周器31から出力された分周後の発振出力信号が、位相周波数比較器13と可変遅延器16と注入制御器18とに入力されてもよい。

### [0052]

また、本実施の形態では、上述のように、図2で示される遅延制御器15において、発 振出力信号及び注入信号の一方をNOT回路21で反転させて位相比較器22に入力する 場合について説明したが、そうでなくてもよい。上述のように、発振出力信号と、注入信 だけ異なっていることが好適であるが、位相比較器22の前段の段階で 号との位相は、 両者の位相が だけ異なるように設定した場合には、それ以降の回路における遅延等に応 じて電圧制御発振器11に注入される時点では、発振出力信号と、注入信号との位相が 以上異なることもあり得る。そのような場合には、電圧制御発振器11への注入時点にお いて、発振出力信号と注入信号との位相差が となるように、位相比較器22より後段の 回路における遅延時間も考慮して、位相比較器22の前段における反転等の処理を行って もよい。具体的には、位相比較器 2 2 の前段において、注入信号を時間 T a だけ遅延させ るようにしてもよい。注入信号側にNOT回路21が存在する場合には、その遅延は、N OT回路21の前段で行われてもよく、または後段で行われてもよい。また、その時間T aは、位相比較器22より後段の回路における遅延時間に相当する時間であることが好適 である。本実施の形態では注入信号の遅延量を自動調整することができるため、このよう にオフセット(Ta)を設定することによって、最適なタイミング調整を行うこともでき るようになる。

### [0053]

また、本実施の形態による自己注入位相同期回路 1 において、各構成要素のうち、アナログでもデジタルでも実現できるものについては、そのどちらで実現されてもよいことは言うまでもない。

# [0054]

また、上記実施の形態において、各処理または各機能は、単一の装置または単一のシステムによって集中処理されることによって実現されてもよく、または、複数の装置または複数のシステムによって分散処理されることによって実現されてもよい。

### [0055]

また、上記実施の形態において、各構成要素間で行われる情報の受け渡しは、例えば、その情報の受け渡しを行う2個の構成要素が物理的に異なるものである場合には、一方の構成要素による情報の出力と、他方の構成要素による情報の受け付けとによって行われてもよく、または、その情報の受け渡しを行う2個の構成要素が物理的に同じものである場合には、一方の構成要素に対応する処理のフェーズから、他方の構成要素に対応する処理のフェーズに移ることによって行われてもよい。

# [0056]

また、上記実施の形態において、各構成要素が実行する処理に関係する情報、例えば、各構成要素が受け付けたり、取得したり、選択したり、生成したり、送信したり、受信したりした情報や、各構成要素が処理で用いる閾値や数式、アドレス等の情報等は、上記説明で明記していなくても、図示しない記録媒体において、一時的に、または長期にわたって保持されていてもよい。また、その図示しない記録媒体への情報の蓄積を、各構成要素、または、図示しない蓄積部が行ってもよい。また、その図示しない記録媒体からの情報の読み出しを、各構成要素、または、図示しない読み出し部が行ってもよい。

#### [0057]

また、上記実施の形態において、各構成要素等で用いられる情報、例えば、各構成要素が処理で用いる閾値やアドレス、各種の設定値等の情報がユーザによって変更されてもよい場合には、上記説明で明記していなくても、ユーザが適宜、それらの情報を変更できるようにしてもよく、または、そうでなくてもよい。それらの情報をユーザが変更可能な場

40

合には、その変更は、例えば、ユーザからの変更指示を受け付ける図示しない受付部と、その変更指示に応じて情報を変更する図示しない変更部とによって実現されてもよい。その図示しない受付部による変更指示の受け付けは、例えば、入力デバイスからの受け付けでもよく、通信回線を介して送信された情報の受信でもよく、所定の記録媒体から読み出された情報の受け付けでもよい。

# [0058]

また、上記実施の形態において、各構成要素は専用のハードウェアにより構成されてもよく、または、ソフトウェアにより実現可能な構成要素については、プログラムを実行することによって実現されてもよい。例えば、ハードディスクや半導体メモリ等の記録媒体に記録されたソフトウェア・プログラムをCPU等のプログラム実行部が読み出して実行することによって、各構成要素が実現され得る。その実行時に、プログラム実行部は、記憶部や記録媒体にアクセスしながらプログラムを実行してもよい。このプログラムは、サーバなどからダウンロードされることによって実行されてもよく、所定の記録媒体(例えば、CD-ROMなどの光ディスクや磁気ディスク、半導体メモリなど)に記録されたプログラムが読み出されることによって実行されてもよい。また、このプログラムは、プログラムプロダクトを構成するプログラムとして用いられてもよい。また、このプログラムを実行するコンピュータは、単数であってもよく、複数であってもよい。すなわち、集中処理を行ってもよく、または分散処理を行ってもよい。

### [0059]

また、本発明は、以上の実施の形態に限定されることなく、種々の変更が可能であり、 20 それらも本発明の範囲内に包含されるものであることは言うまでもない。

【産業上の利用可能性】

### [0060]

以上より、本発明による自己注入位相同期回路によれば、位相ノイズを低減できるという効果が得られ、位相同期回路(PLL)として有用である。

### 【符号の説明】

### [0061]

- 1 自己注入位相同期回路

- 11 電圧制御発振器(VCO)

- 12、31 分周器

- 13 位相周波数比較器(PFD)

- 14 電圧発生器

- 15 遅延制御器

- 16 可变遅延器

- 17 切替器

- 18 注入制御器

- 19 チャージポンプ(CP)

- 20、23 ループフィルタ(LPF)

- 2 1 NOT回路

- 2 2 位相比較器 ( P D )

- 3 2 パルス発生器

- 3 3 ノイズ検出器

- 3 4 強度制御器

### フロントページの続き

# (56)参考文献 特開平03-189966(JP,A)

特開2016-201685(JP,A)

特開2010-258516(JP,A)

Shwetabh Verma et al. , A Unified Model for Injection Locked Frequency Dividers , IEEE J ournal of Solid State Circuits , 米国 , IEEE , 2 0 0 3 年 6月, Vol.38, No.6 , pp1015 102 7

Chih Lu Wei et al., , A Subharmonically Injection Locked PLL With Calibrated Injection Pulsewidth , IEEE Transactions on Circuits and Systems II:Express Briefs ,米国,IEEE,2 0 1 5 年 6 月,Vol.62, No.6,pp.548 552

### (58)調査した分野(Int.Cl., DB名)

H 0 3 L 1 / 0 0 - 9 / 0 0

IEEE Xplore